YosysHQ

@yosyshq

Sign up to our newsletter! yosyshq.com/newsletter

ID: 1337100214881185794

https://www.yosyshq.com/ 10-12-2020 18:22:24

315 Tweet

3,3K Followers

15 Following

Today I visited @[email protected]. 🚂 First time trying an #FPGA with the @1bitsquared but not here #OrangeCrab board, #UX is superb with YosysHQ and #Amaranth. PRs filed for supporting the 85F variant 👩💻 Blinky was up and running in no time. 👍 Huge thanks to everyone developing the awesome tools! 🧡

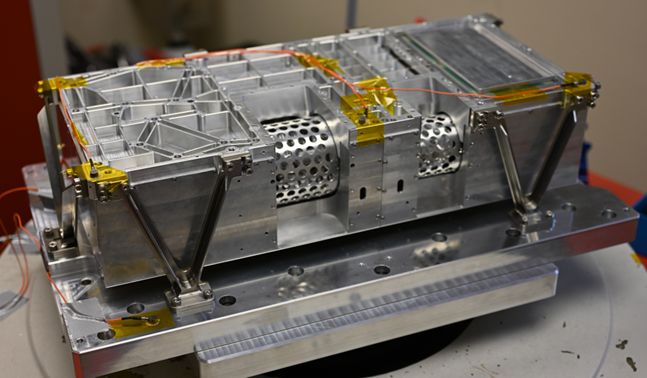

#FPGA tt02-s4ga works. I have streamed several netlists’ bitstreams into the design and so far all is well. A 283 5-LUT, 376 milliHertz FPGA datapath (2.5 kHz SoC clk) in ~150x170um of Skywater 130nm. github.com/grayresearch/t… Thanks again Tiny Tapeout efabless.com YosysHQ OpenROAD…

We (and I cannot stress this enough) are so back. Jumperless V5 lets you prototype like a nerdy wizard that can see electricity and conjure jumpers wherever you want. And the wait is nearly over for this particular superpower, it launches September 23rd on Crowd Supply.

I can't believe I dared to do it: an iCE40HX8K FPGA that boots a mainline 6.13.0-rc1 #Linux kernel via OpenSBI, running 100% KianV SV32 (MMU) RV32IMA Zicntr Zicsr Zifencei SSTC RISC-V. Incredible... amazing board, thanks to Machdyne UG's Kuchen iCE40HX8K FPGA board. #ice40 RISC-V International