Nils Wistoff

@niwist

PhD Student at ETH Zurich

ID: 703010660200882178

26-02-2016 00:16:17

21 Tweet

70 Followers

36 Following

Nils Wistoff from ETH Zurich talking about adding hardware support for preventing running channels on RISC-V International #seL4 #Summit

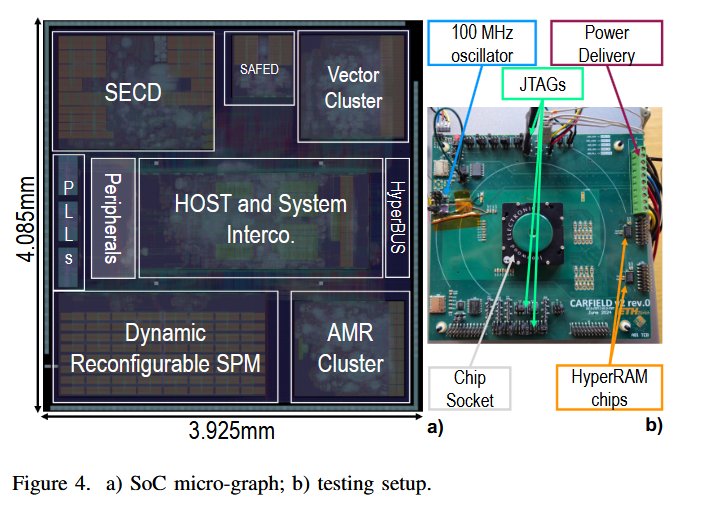

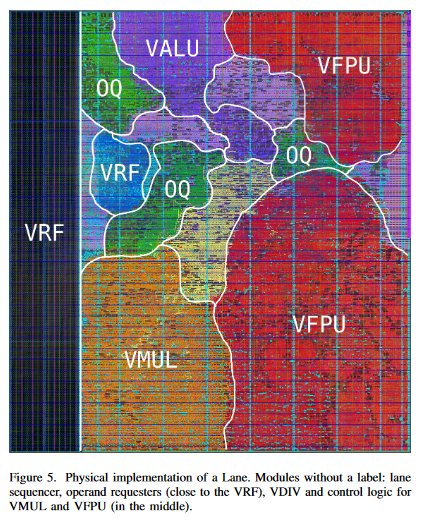

For all the fans of vector architectures, our paper titled "A “New Ara” for Vector Computing: An Open Source Highly Efficient RISC-V V 1.0 Vector Processor Design" 🦜is now on arxiv. Check it out: arxiv.org/pdf/2210.08882… Matteo Perotti @suehtamacv Nils Wistoff Lukas

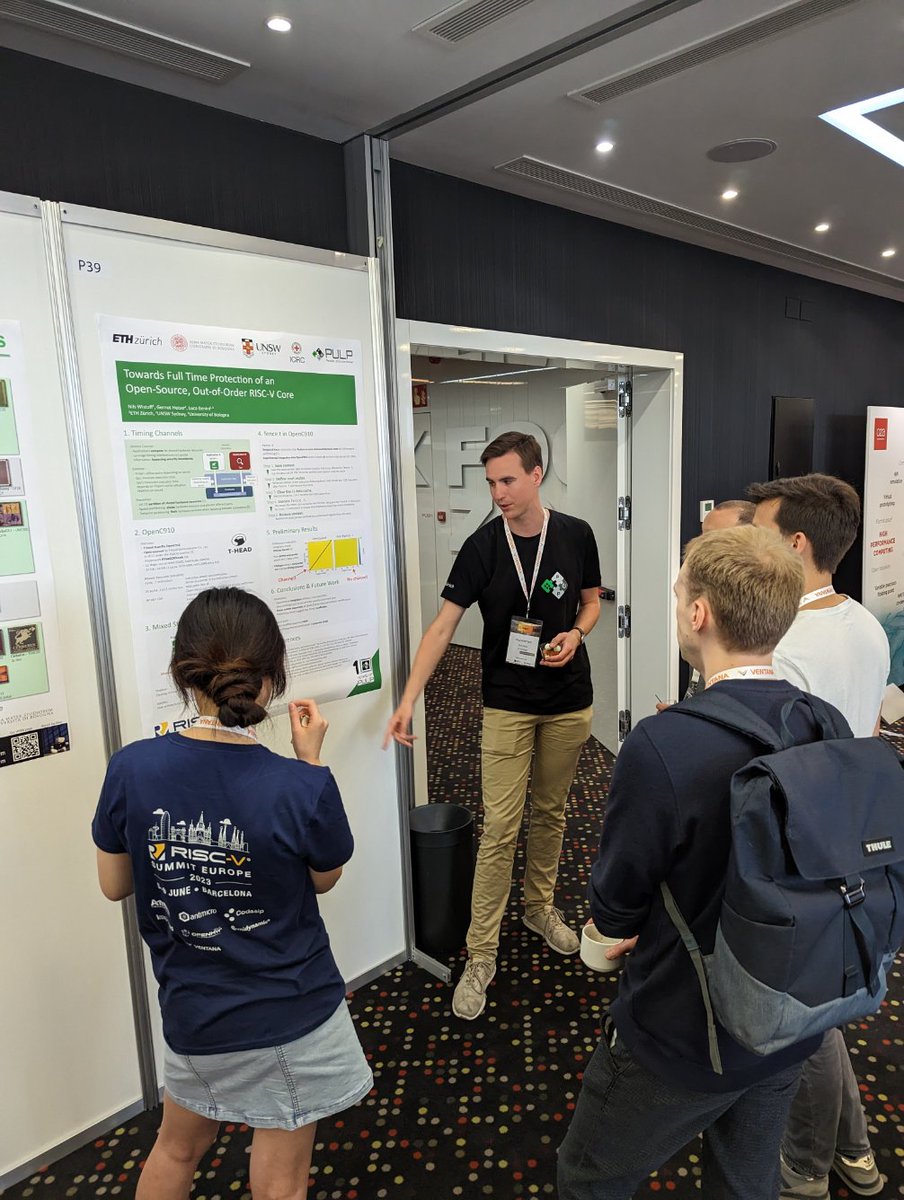

There is so much to learn at the poster session of #RISCVSummitEurope in Barcelona. Nils Nils Wistoff just presented "Towards Full Time Protection of an Open-Source, Out-of-Order RISC-V Core" with fence.t instruction inside 😀: riscv-europe.org/media/proceedi… riscv-europe.org/media/proceedi…

Nice one! The paper "Towards a RISC-V Open Platform for Next-generation Automotive ECUs" just won Distinguished Paper in Cyber-Physical Systems and Internet-of-Things (CPS&IoT’2023) Award. Congratulations to Luca, Claudio, Alessandro Ottaviano, Nils Wistoff & Robert mecoconference.me/4028/meco2023-…

Reporting from MICRO in Toronto, here is the talk on "AutoCC: Automatic Discovery of Covert Channels in Time-Shared Hardware" with Marcelo Marcelo Orenes-Vera and our Nils Nils Wistoff during the poster session. Check out the repo github.com/morenes/AutoCC and the paper: parallel.princeton.edu/papers/micro23…

Don't forget to come by and meet PULP team members Michael Rogenmoser, Emanuele, Thomas Benz, Nils Nils Wistoff, Simone and Frank at the poster sessions of #RISCV Summit Europe in Munich🇩🇪🍺. Check out the schedule below: riscv-europe.org/summit/2024/po… Looking forward!

Aloha! Gianna Paulin just presented our 432-core #RISCV Based dual Chiplet Occamy in 12nm FinFET at IEEE Symposium on VLSI Technology & Circuits in Hawaii.

Our paper on "Occamy: A 432-Core 28.1 DP-GFLOP/s/W 83% FPU Utilization Dual-Chiplet, Dual-HBM2E RISC-V-based Accelerator for Stencil and Sparse Linear Algebra Computations with 8-to-64-bit Floating-Point Support in 12nm FinFET" is on arXiv: arxiv.org/pdf/2406.15068 Gianna Paulin

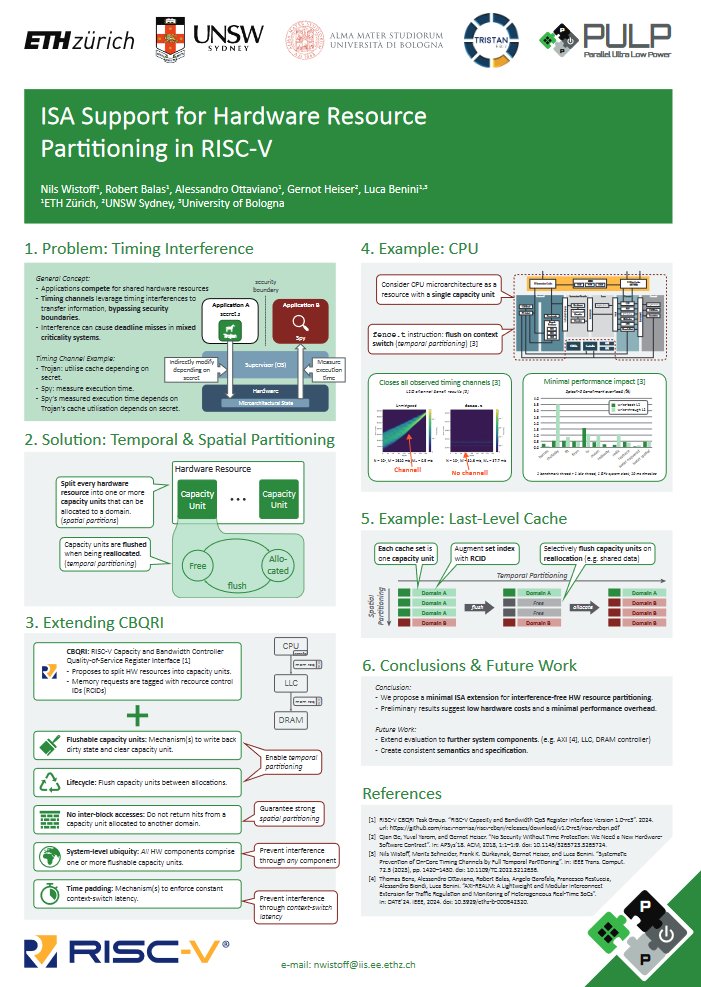

Poster session is on at the #RISCV Summit in Munich! Nils Nils Wistoff presents his work on ISA Support for Hardware Resource Partitioning in RISC-V. Find his poster here: pulp-platform.org/docs/riscvmuni…

Spotted at the aerodrome of GAP, France... surely this can't be a coincidence🤔Nils Wistoff Florian Zaruba en.wikipedia.org/wiki/Gap%E2%80… jetphotos.com/registration/F…

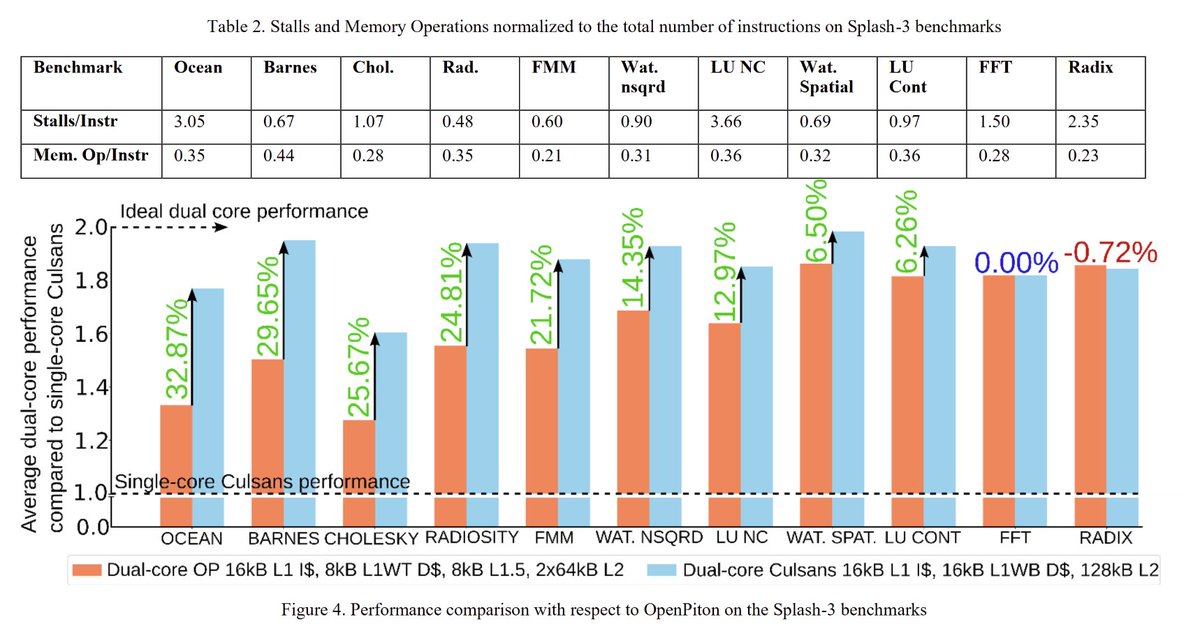

Existing multi-core cache-coherent RISC-V platforms are complex and not efficient for small embedded core clusters. We propose "Culsans: An Efficient Snoop-based Coherency Unit for the CVA6 Open Source RISC-V application processor" See arxiv.org/pdf/2407.19895 Luca Valente

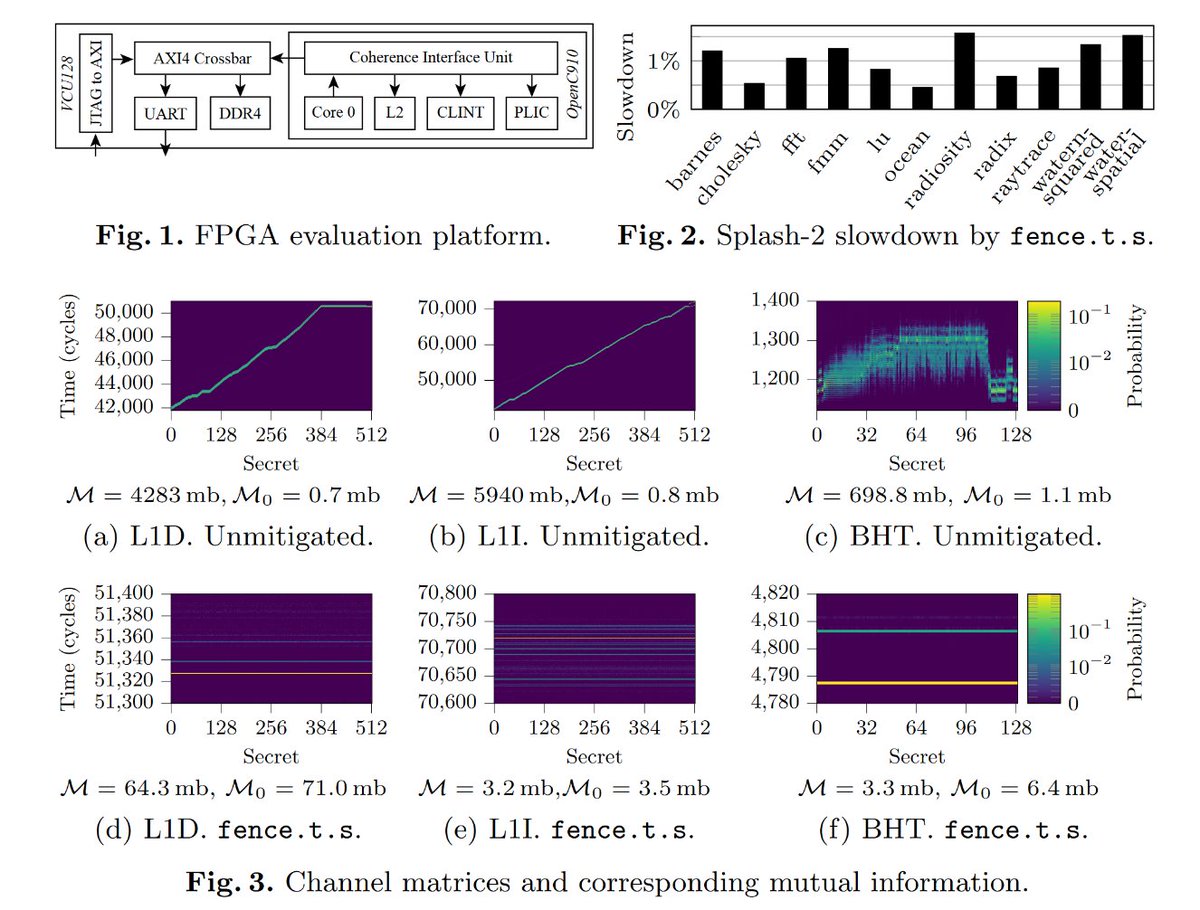

We propose an SW-supported temporal fence (fence.t.s) that closes timing channels even in complex Out-of-Order cores. See Nils Wistoff's "fence.t.s: Closing Timing Channels in High-Performance Out-of-Order Cores through ISA-Supported Temporal Partitioning" arxiv.org/pdf/2409.07576

The ApplePies conference on Applications in Electronics just took place in Turin. Our Nils Nils Wistoff was there presenting "fence.t.s: Closing Timing Channels in High-Performance Out-of-Order Cores through ISA-Supported Temporal Partitioning". Get the slides: pulp-platform.org/docs/applepies…

Here it is! Our paper "Occamy: A 432-Core Dual-Chiplet Dual-HBM2E 768-DP-GFLOP/s RISC-V System for 8-to-64-bit Dense and Sparse Computing in 12nm FinFET" accepted for publication in IEEE JSSC is now on arXiv: arxiv.org/pdf/2501.07330 Thomas Benz Viviane Potocnik Nils Wistoff

Nils Nils Wistoff, Cyril and Frank have just visited Friedrichshafen to discuss possible future collaboration with ZF zf.com/mobile/en/home… . Below a couple of pics from the visit, and of course the iconic Zeppelin.