Samuel

@saem_r

PhD Student at ETH Zurich

ID: 719889681320689664

12-04-2016 14:07:29

18 Tweet

63 Followers

68 Following

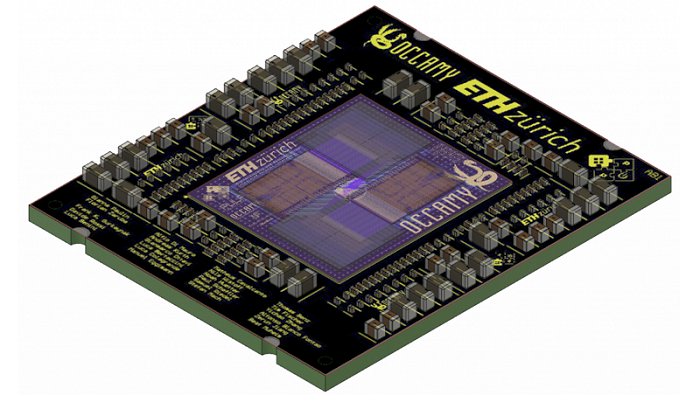

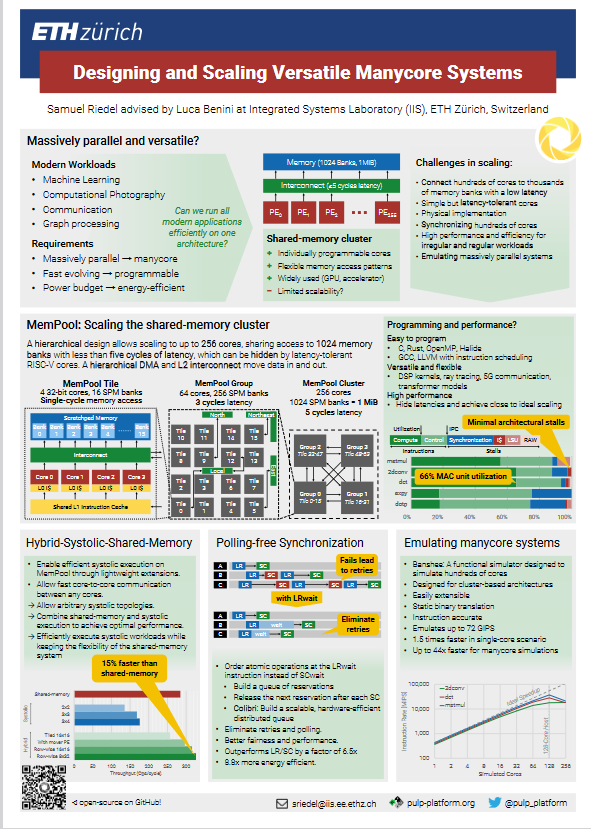

Just in time for Valentine’s Day, here comes the first PULP chip of the year: Heartstream in GF12. An implementation of our MemPool architecture with 64 RISC-V cores. Supported by GlobalFoundries UPP asic.ethz.ch/2024/Heartstre…

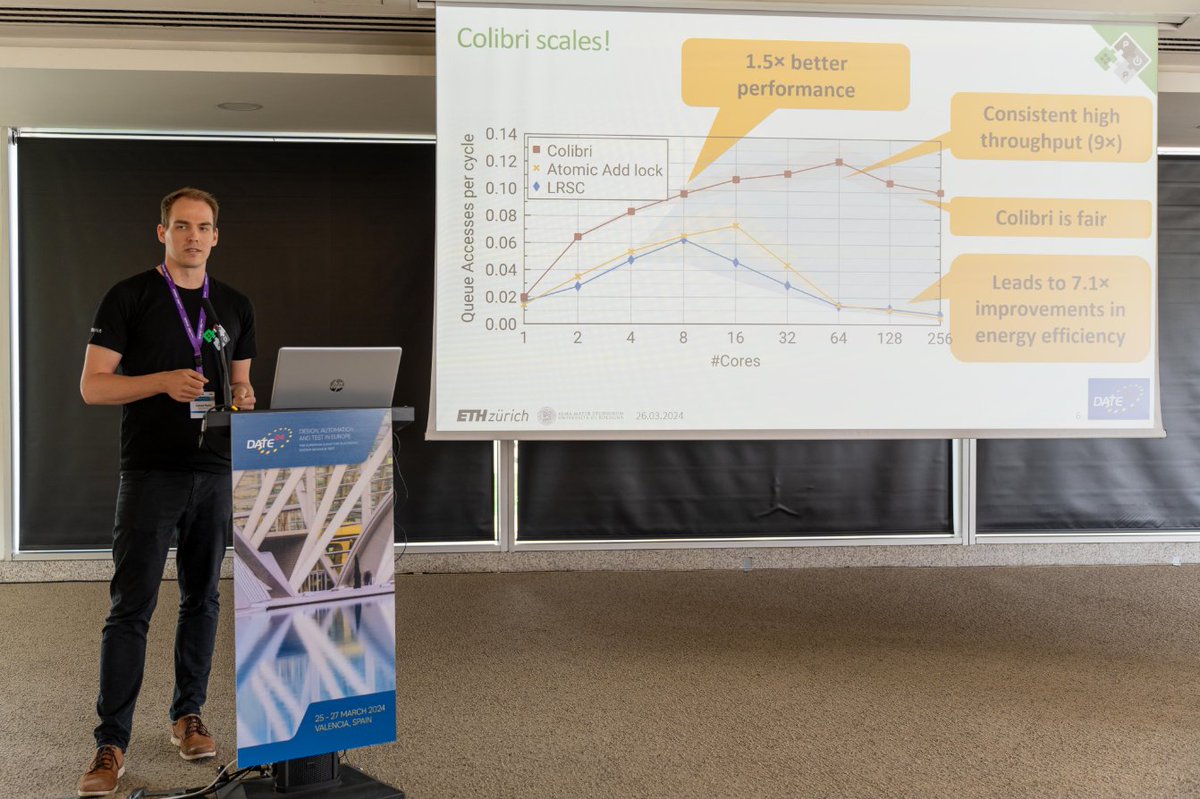

Samuel Samuel presented LRSCwait where we introduce new atomic operations to eliminate polling and retries during synchronization in manycore systems: arxiv.org/abs/2401.09359 pulp-platform.org/docs/date2024/… Big thank you to Samuel for doing such an amazing job reporting from #DATE2024.

While Charlie the bear was busy in Zurich, our #DATE2024 team enjoyed one last 🌞😎 day with El Oso Valenciano 🧸🇪🇸 Samuel Luca Colagrande Cristian Cioflan Thomas Benz.

Here we come with Heartstream and Charlie The Bear in full beauty: How to tape-out a 64-core RISC-V SoC in under 60 days pulp-platform.org/docs/riscvmuni… Paper: pulp-platform.org/docs/riscvmuni… Sergio Mazzola Yichao, Zhang Samuel Marco Bertuletti just presented at #RISCV Summit in Munich.

Thank you so much to the whole PULP Platform group and everyone else for supporting me over the past years and for celebrating this moment with me! 🙌

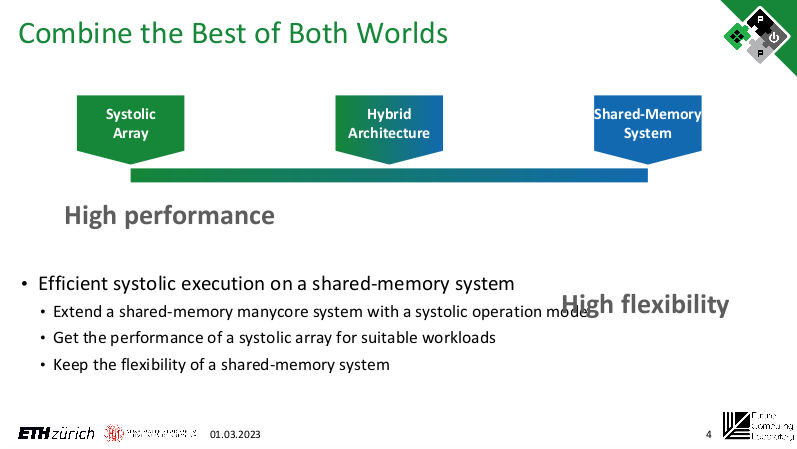

Great joy at IIS! Our Heartstream 🤎 chip in GF12 with 64 cores, floating point support & systolic extension says "Hello" after Marco Bertuletti, Samuel Samuel and Yichao Yichao, Zhang, got the Serial Link, JTAG, and UART running. Cheers to that! asic.ethz.ch/2024/Heartstre… Sergio Mazzola