Yichao, Zhang

@yichao_zh

An IC Design PhD student in the PULP project @ETH Zurich

ID: 1368032426845302785

06-03-2021 02:55:30

22 Tweet

52 Followers

35 Following

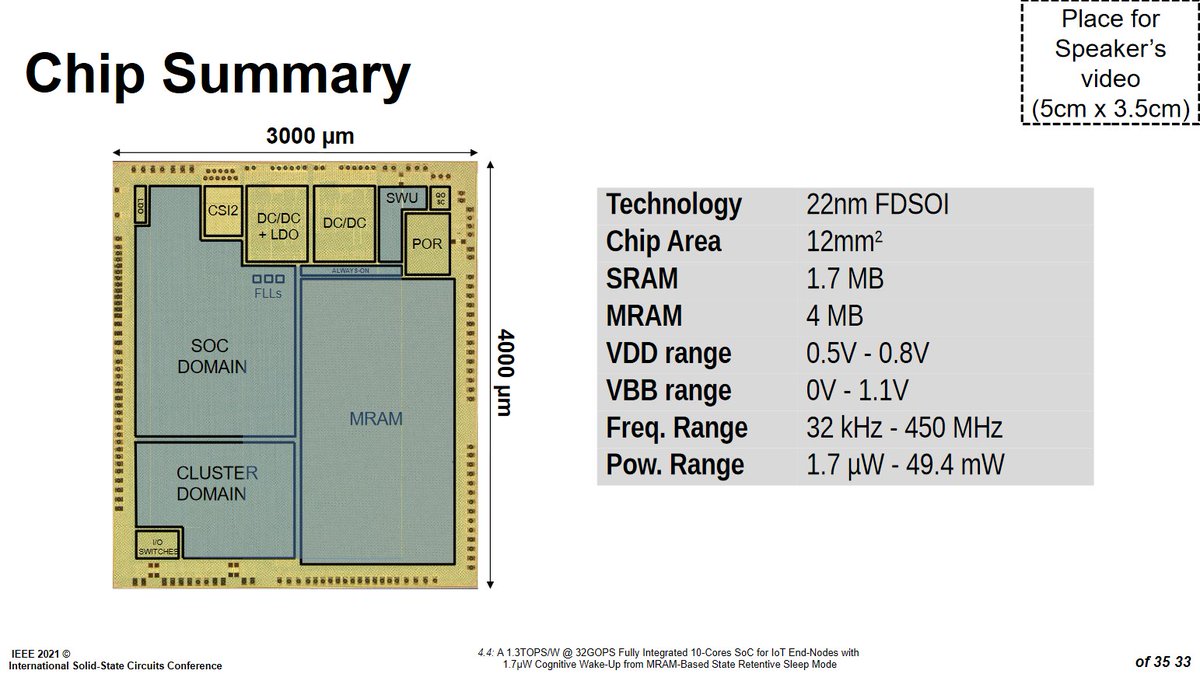

We are proudly sharing the slides of our VEGA-related talk that made it into #ISSCC2021 "A 1.3TOPS/W @ 32GOPS Fully Integrated 10-Cores SoC for IoT End-Nodes with 1.7μW Cognitive Wake-Up from MRAM-Based State Retentive Sleep Mode" by Davide Rossi 💇♂️😇& Co pulp-platform.org/docs/isscc2021…

The two-week countdown to the 2nd #RISC-V week just started ⏱️😀. Expect The Best. Luca Luca Benini will give a keynote on PULP in his keynote titled "Seven Chips in Seven Years" on March 31, 2021. Check out the schedule and register open-src-soc.org/2021-03/progra…

Serious brainstorming is under way during the creative labs at the Cyber-Physical Systems Summer School in Pula, Sardinia 😅💦@CPSschool22. Divided into groups of five the teams are supposed to design an FPGA-based CPS. Good luck, PULP team members! Marco Bertuletti Yichao, Zhang

Intrigued about what our MemPool and TeraPool can do for you? Learn more in our latest paper "Efficient Parallelization of 5G-PUSCH on a Scalable RISC-V Many-core Processor" on arXiv: arxiv.org/pdf/2210.09196… Marco Bertuletti Yichao, Zhang

Just in time for Valentine’s Day, here comes the first PULP chip of the year: Heartstream in GF12. An implementation of our MemPool architecture with 64 RISC-V cores. Supported by GlobalFoundries UPP asic.ethz.ch/2024/Heartstre…

Our "TeraPool-SDR: An 1.89TOPS 1024 RV-Cores 4MiB Shared-L1 Cluster for Next-Generation Open-Source Software-Defined Radios" by Yichao, Zhang landed with Marco Bertuletti in Tampa FL where it was presented at #GLSVLSI2024. Learn more dl.acm.org/doi/10.1145/36… & pulp-platform.org/docs/glsvlsi20…

You can now find "A 1024 RV-Cores Shared-L1 Cluster with High Bandwidth Memory Link for Low-Latency 6G-SDR" abstract extension accepted to the VLSISOC24 PhD forum on arXiv: arxiv.org/pdf/2408.08882 Yichao, Zhang Marco Bertuletti Samuel Alessandro Vanelli-Coralli

Our Yichao Yichao, Zhang is currently in Tanger 🇲🇦 attending VLSI-SoC. You can find his poster & paper on TeraPool "1024 RV-Cores Shared-L1 Cluster with High Bandwidth Memory Link for Low-Latency 6G-SDR" here: pulp-platform.org/docs/vlsisoc20… pulp-platform.org/docs/vlsisoc20… Marco Bertuletti Samuel

Wonderful news from Tangier! Our paper on TeraPool "A 1024 RV-Cores Shared-L1 Cluster with High Bandwidth Memory Link for Low-Latency 6G-SDR" just won the Best PhD forum Award at VLSI-SoC 2024. Below Yichao Yichao, Zhang with Henk Corporaal 🇳🇱 & Said Hamdioui receiving the award🏆.

Congrats to Yichao! Serious work being done by PULP Platform to enable ultimate scaling of large RISC-V International processor clusters and their applications, from AI to radio access networks (RANs)! github.com/pulp-platform/…

Great joy at IIS! Our Heartstream 🤎 chip in GF12 with 64 cores, floating point support & systolic extension says "Hello" after Marco Bertuletti, Samuel Samuel and Yichao Yichao, Zhang, got the Serial Link, JTAG, and UART running. Cheers to that! asic.ethz.ch/2024/Heartstre… Sergio Mazzola

We are sharing a couple of pics from Yichao's Yichao, Zhang recent talk "The Open-Source IC Design: From Architecture to Tape-out in PULP Platform" for the Chinese Science Club Zurich dealing with chip design, design flow & our projects i.e. Occamy, TeraPool, HeartStream & Basilisk.